Процессоры AMD EPYC 4 поколения

15.09.23

10 ноября 2022 года корпорация AMD анонсировала выпуск серверных процессоров EPYC серии 9004, основанных на микроархитектуре Zen4. AMD продолжает делать ставку на наращивание количества ядер и объема кэша для 1- и 2-процессорных систем. Максимальное число ядер в первоначально вышедшей линейке процессоров — 96, а после появления в июне 2013 процессоров с микроархитектурой Zen4c — 128.

Процессор AMD EPYC 9654. © ServeTheHome.

Кодовое название новой серии процессоров — Genoa («Генуя»). AMD продолжает традицию названий по итальянским городам. Предыдущие процессоры были названы в честь Рима, Неаполя и Милана.

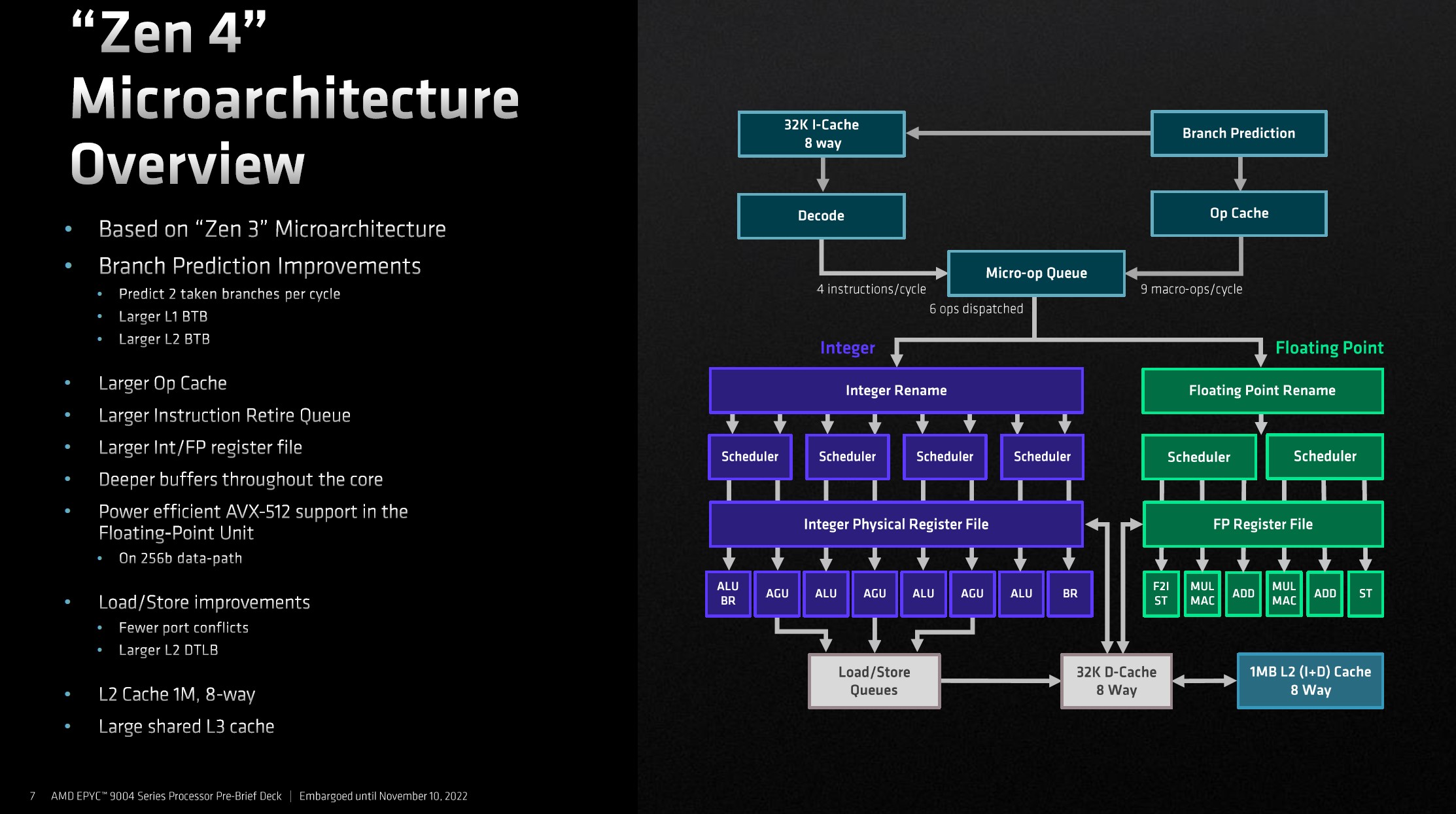

EPYC 4-го поколения — это не просто экстенсивное улучшение предыдущей архитектуры Zen3 за счет уменьшения техпроцесса (переход на 5 нм вместо 7) и оптимизации архитектуры. Улучшение блоков предсказания ветвлений, увеличение объема кэша L2 и другие изменения позволили получить небольшой прирост, около 14%, производительности на ядро в сравнении с Zen3. Но основные улучшения Zen4 заключаются в другом:

- Рост плотности размещения ядер (в 1,5, затем в 2 раза — с 64 до 128 ядер).

- Рост пропускной способности памяти. Вместо 8 каналов DDR4-3200 теперь 12 каналов DDR5-4800. Пропускную способность и объем можно увеличить дополнительно за счет подключения устройств CXL, о которых мы расскажем ниже.

- Рост пропускной способности ввода-вывода за счет перехода на PCIe 5.0.

PCIe 5.0

Теоретическая пропускная способность нового поколения PCI Express удвоилась в сравнении с PCIe 4.0 — до 32 Гбит/с без учета кодирования. Пропускная способность 16 линий составляет внушительные 63 ГБ/с.

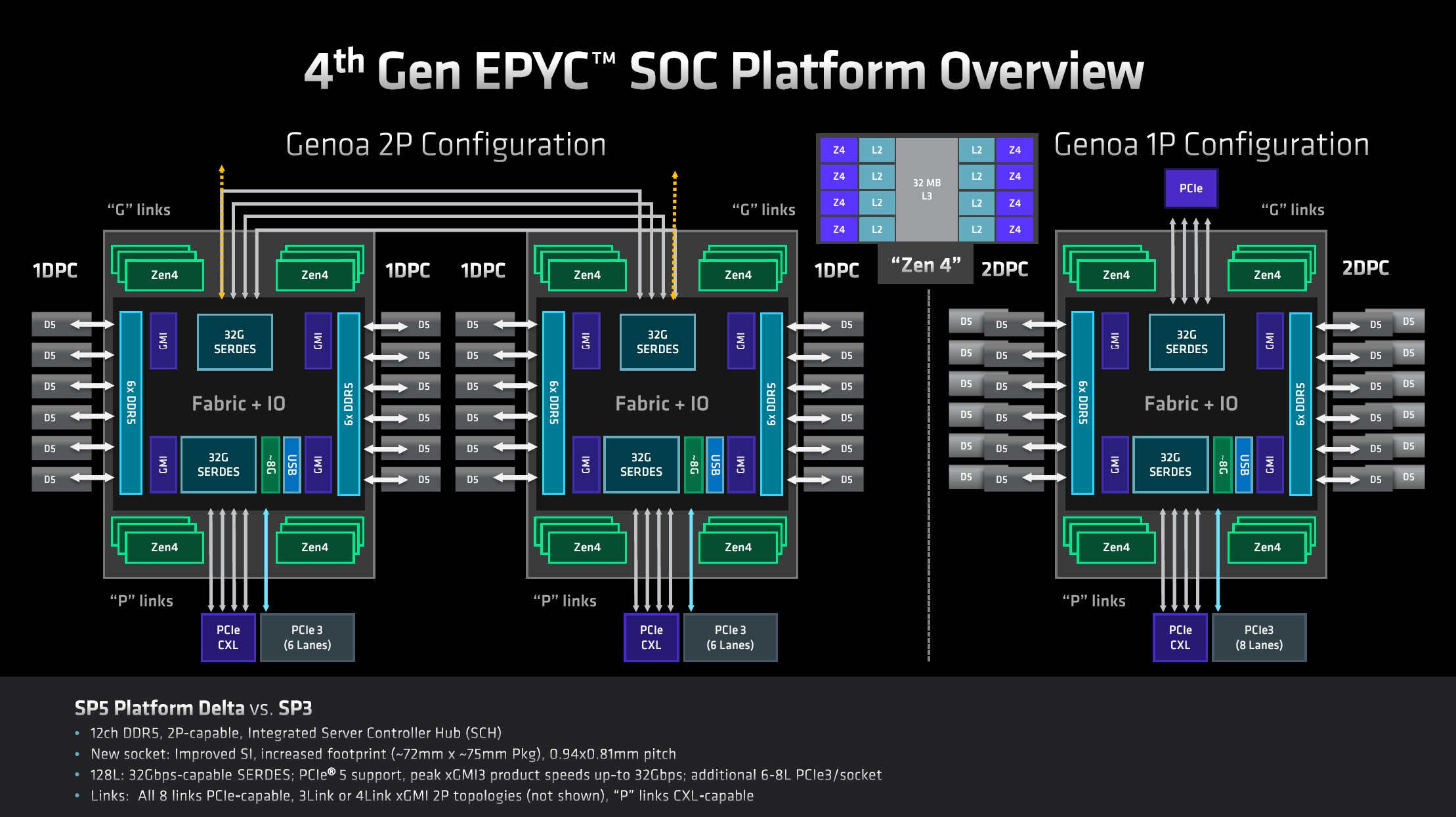

Наращивание плотности размещения ядер влияет на доступную пропускную способность ввода-вывода. Дело в том, что процессоры с большим количеством ядер состоят не из одного монолитного блока. Процессорные ядра сгруппированы по 8 на модуле CCD (Сore Сomplex Die) в процессорах Genoa или по 16 в появившихся летом процессорах Bergamo. Например, в 96-ядерном AMD EPYC 9654 используется 12 8-ядерных CCD. Блоки CCD подключены к блоку ввода-вывода (I/O die) через шину GMI3. Хорошая новость заключается в том, что процессоры с «небольшим» числом ядер (до 32) с 4 CCD используют два линка GMI3 на каждый CCD вместо одного.

Для соединения процессоров в 2-процессорных конфигурациях используется Infinity Fabric, но соответствующие блоки SerDes являются универсальными — они могут работать в режиме PCI Express. Это дает интересную возможность производителям материнских плат. Процессоры позволяют выбрать между 3 и 4 линками Infinity Fabric. Сэкономленный линк можно задействовать под дополнительные 16 линий PCIe 5.0 и получить таким образом в 2-процессорной системе 160 линий вместо 128.

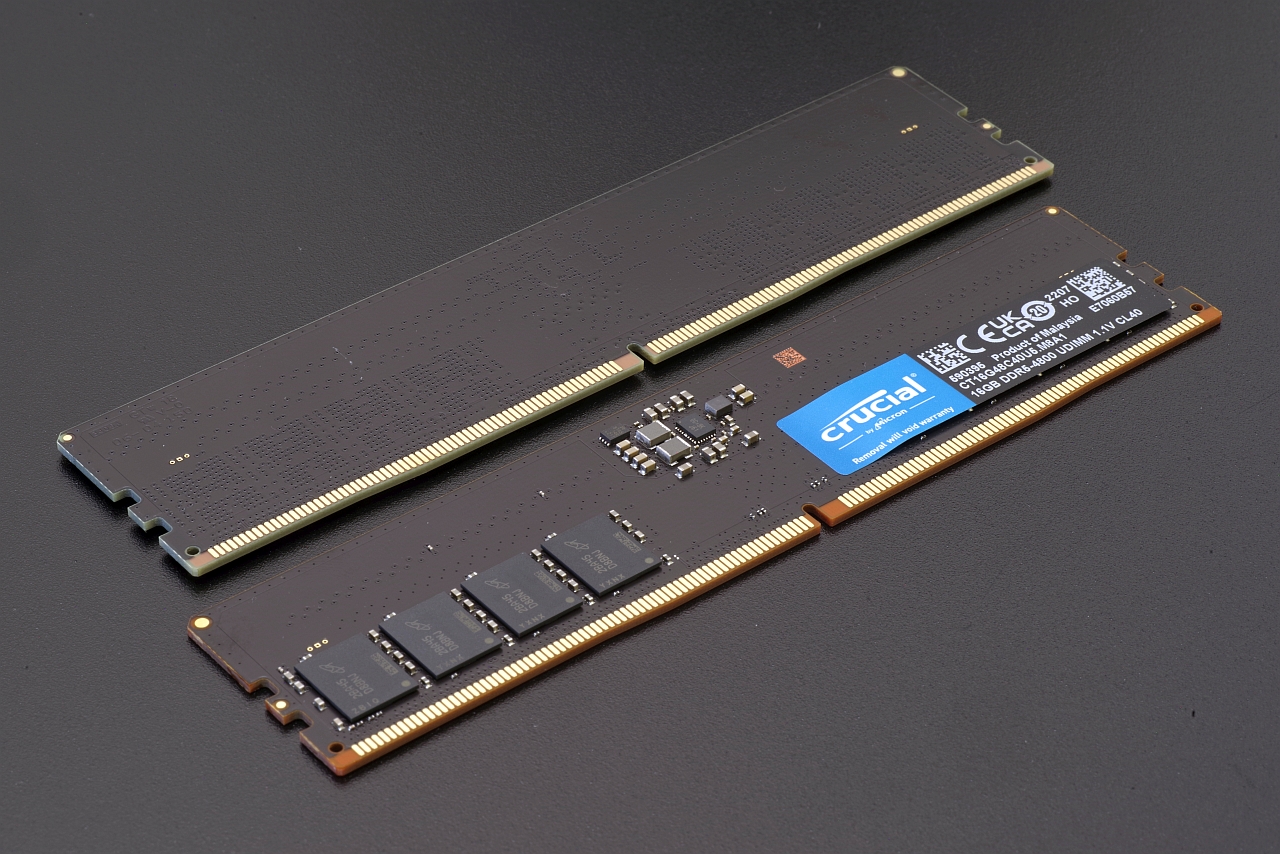

DDR5

В сравнении с DDR4 мы получаем даже на старте увеличение пропускной способности в 1,5 раза — с 3,2 до 4,8 ГБ/с на модуль для поддерживаемой новыми процессорами AMD DDR5-4800. Прогнозируется дальнейшее увеличение пропускной способности. Сейчас уже есть образцы серверных модулей 5600 и 6400 МБ/с, в дальнейшем планируется до 8400 МБ/с.

Модуль памяти DDR5. © Wikimedia Foundation.

Уменьшение техпроцесса вместе с наращиванием объема памяти отрицательно сказывается на надежности. Для решения этой проблемы применяется коррекция ошибок на уровне чипа (On-Die ECC) по схеме 128+8. Внутричиповый ECC не отменяет необходимости в традиционном ECC на уровне модулей для серверной памяти.

К сожалению, стоит DDR5 сейчас существенно дороже. Например, модули 64 ГБ RDIMM обойдутся в два раза дороже, чем DDR4. Производители пытаются сгладить эту разницу за счет выпуска модулей нестандартного объёма — 48 и 96 ГБ.

Существующие на данный момент материнские платы для AMD EPYC 4-го поколения поддерживают 1 или 2 модуля на канал, объём — до 6 ТБ на процессор. Вместе с увеличением количества каналов быстрая DDR5 обеспечивает более чем 2-кратный рост пропускной способности памяти, но при небольшом увеличении задержки — со 105 до 118 нс. При установке 2 модулей на канал максимальная частота работы памяти снижается до 4000 или 3600 (при использовании 1-ранговых и 2-ранговых модулей соответственно).

CXL (Compute Express Link)

Compute Express Link — высокоскоростной интерфейс для подключения устройств ввода-вывода и памяти. Спецификация первой версии стандарта CXL появились в 2019 году, а поддержка со стороны серверных платформ повилась в последних поколениях процессоров AMD и Intel. Особенность CXL заключается в том, что он работает поверх PCI Express, и для получения достаточной пропускной способности потребовалось дождаться появления PCIe 5.0.

Процессоры AMD EPYC 9004 поддерживают устройства класса CXL.mem, то есть устройства, обеспечивающие простое расширение оперативной памяти. Такие устройства в поддерживаемых ОС выглядят, как дополнительный узел NUMA, содержащий только память, без своего процессора.

Для CXL в процессоре можно выделить до 64 линий, а одно CXL устройство, подключаемое через 16 линий, получает пропускную способность, приблизительно соответствующую двум каналам DDR5 при уровне задержек 170–250 нс (в 1,5–2 выше в сравнении с памятью, подключаемой к контроллеру процессора). То есть память, подключаемая через CXL рассматривается инженерами в качестве еще одного уровня в иерархии — между NVMe и подключаемой напрямую DRAM.

Модуль памяти DDR5 CXL EDSFF. © Samsung.

Прототипы модулей DDR5 объемом 512 ГБ уже представили Samsung и Hynix. Модули выполнены в форм-факторе EDSFF, который уже применяется для SSD. Впрочем, использование определенного форм-фактора не является обязательным, устройства CXL могут быть выполнены и в виде плат расширения PCIe.

Теоретически, при использовании 4 устройств CXL.mem для 1-процессорной системы мы можем получить в дополнение к штатным 12 каналам DDR5 ещё 8.

Обновление: процессоры Bergamo

13 июня 2023 года были анонсированы процессоры под кодовым названием Bergamo. Инженерам AMD удалось уменьшить площадь, занимаемую ядром Zen4 на 35% за счет оптимизации и уменьшения размера кэшей, что позволило разместить в одном корпусе 128 ядер.

Блоки CCD вместо 8-ядерных стали 16-ядерными, новые процессоры используют 7 или 8 таких блоков (112 или 128 ядер). Основное применение этих процессоров — крупные облачные проекты, где требуется постоянное наращивание плотности размещения вычислительных ресурсов.

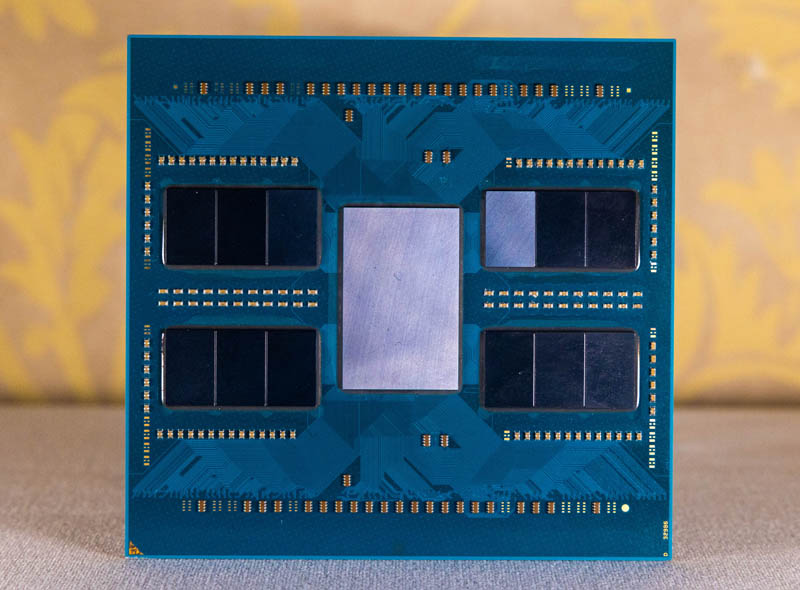

Процессор AMD EPYC серии Genoa-X со снятой крышкой. © ServeTheHome.

Одновременно были представлены три процессора серии Genoa-X, в которых была применена технология 3D V-Cache, ранее уже опробованная на процессорах Ryzen последнего поколения и серверных EPYC серии Milan-X. Площадь кристалла всегда была основным фактором, ограничивающим объем кэш-памяти. В процессорах с 3D V-Cache дополнительный объем кэша L3 находится на отдельном кристалле, который смонтирован поверх CCD. В случае с AMD Bergamo применение данной технологии позволило на той же площади получить гигантский кэш L3 — более 1 гигабайта в максимальной конфигурации (96-ядерный EPYC 9684X). Еще два процессора, 16-ядерный 9184X и 32-ядерный 9384X получили по 768 МБ кэша L3 вместо 256 МБ у обычных процессоров с аналогичным количеством ядер из этой линейки.

Платформы Supermicro H13

Платформа Supermicro AS-2125HS-TNR. © Super Micro Computer, Inc.

Компания Supermicro выпустила большое количество платформ под новое поколение процессоров EPYC. Их можно разделить на 4 группы (модульные решения, Twin, MicroCloud мы рассматривать не будем из-за логистических трудностей):

- H13 CloudDC. Бюджетные серверы общего назначения. 12 DIMM, опциональная поддержка NVMe:

- AS-1015CS-TNR. 1U, 4x 3.5", 2 слота PCIe x16

- AS-1115CS-TNR. 1U, 8x 2.5", 2 слота PCIe x16.

- AS-2015CS-TNR. 2U, 12x 3.5", 4 слота PCIe x16.

- H13 Hyper. Однопроцессорные серверы с 24 DIMM и штатной поддержкой NVMe:

- AS-1115HS-TNR. 1U, 8x 2.5", 3 слота PCIe x16

- AS-2015HS-TNR. 2U, 12x 3.5", 4 слота PCIe x16 (с возможность сконфигурировать до 8 слотов x8 в разных сочетаниях).

- AS-2115HS-TNR. 2U, 24x 2.5", 4 слота PCIe x16 (с возможность сконфигурировать до 8 слотов x8 в разных сочетаниях), количество доступных слотов PCIe зависит от количества используемых накопителей NVMe.

- H13 Hyper-U. Двухпроцессорные серверы:

- AS-1125HS-TNR. 1U, 8x 2.5", 3 слота PCIe x16

- AS-2025HS-TNR. 2U, 12x 3.5", 4 слота PCIe x16 (с возможность сконфигурировать до 8 слотов x8 в разных сочетаниях).

- AS-2125HS-TN. 2U, 24x 2.5", 4 слота PCIe x16 (с возможность сконфигурировать до 8 слотов x8 в разных сочетаниях), количество доступных слотов PCIe зависит от количества используемых накопителей NVMe.

- H13 All-Flash EDSFF. Однопроцессорные серверы с поддержкой устройств форм-фактора EDSFF (накопителей NVMe и устройств CXL):

- ASG-1115S-NE316R. 1U, 16x EDSFF, 2 слота PCIe x16

- ASG-2115S-NE332R. 2U, 32x EDSFF, 2 слота PCIe x16.

Ссылки:

- Пресс-релиз AMD. AMD EPYC 9004 Series Architecture Overview. Обзор архитектуры процессоров AMD EPYC серии 9004. Содержит важную информацию о топологии CCD/CCX, контроллера памяти и возможностях настройки топологии NUMA (Numa Nodes Per Socket, LLC as NUMA).